1.5 Proyecto Vivado

1.5.1 Inicio del proyecto

Un proyecto agrupa toda la información relacionada con el diseño de un sistema digital que se implementa en una FPGA, incluyendo los archivos de código fuente, los testbenches y las restricciones de diseño.

Para crear el proyecto Vivado, seguiremos los siguientes pasos:

Crear la estructura de carpetas del proyecto:

(este apartado ya está realizado en el espacio de trabajo proporcionado)

Utilizaremos la estructura de carpetas descrita siguiente:

<NombreDelProyecto>/ # Carpeta raíz del proyecto ├───rtl/ # Código fuente módulos VHDL ├───sim/ # Test-benches VHDL ├───constraints/ # Archivos de restricciones ├───scripts/ # Scripts de automatización └───vivado/ # Proyecto VivadoSituaremos los códigos VHDL que modelan los distintos módulos en la carpeta

./rtl, los testbenches en la carpeta./simy las restricciones de pines y temporización en la carpeta./constraints.En la carpeta

./scriptssituaremos el scriptlab.tclpara crear el proyecto Vivado.El código del script es el siguiente

# ================================================================== # Script Tcl para Vivado - labs 30315 Part: xc7a35tcpg236-1 (Basys3) # ================================================================== # 0. Configuración básica set script_dir [file dirname [info script]] # 1. Crear proyecto y cambia a la carpeta del proyecto create_project lab "$script_dir/../vivado" -part xc7a35tcpg236-1 -force set project_dir [get_property DIRECTORY [current_project]] cd $project_dir # 2. Configuración del proyecto para trabajar con VHDL set_property target_language VHDL [current_project] set_property simulator_language VHDL [current_project] # 3. Añadir fuentes de diseño, situadas en la carpeta rtl add_files [file normalize "$project_dir/../rtl"] # 4. Añadir archivos de testbench, situados en la carpeta sim add_files -fileset sim_1 [file normalize "$project_dir/../sim"] # 5. Añadir archivos de restricciones, situados en la carpeta constraints add_files -fileset constrs_1 [file normalize "$project_dir/../constraints"] # 5.1 EL fichero de localizaciones no se usa en síntesis set_property used_in_synthesis false [get_files "$script_dir/../constraints/02_basys3_io.xdc"]Puedes consultar en Vivado Design Suite Tcl Command Reference Guide, los detalles sobre los comandos tcl [1] utilizados.

Abrir Vivado Design Suite y ejecutar el script Tcl para crear el proyecto:

Para ejecutar este script:

Lanza Vivado Design Suite.

En el menú principal :

En el cuadro de diálogo que aparece, navega hasta la carpeta

./scriptsy abre el archivo./scripts/lab.tcl.De esta forma se creará un nuevo proyecto en la carpeta

./vivadocon el nombrelab, y se abrirá automáticamente .

Una vez creado el proyecto, puedes abrirlo en cualquier momento desde Vivado, o

haciendo doble clic en el archivo lab.xpr que se encuentra en la carpeta

./vivado.

Si necesitas volver a crear el proyecto, puedes ejecutar de nuevo

el script Tcl. No se perderán los archivos del diseño puesto que se encuentran

fuera de la carpeta ./vivado. Esto puede resultar útil si necesitas cambiar

de versión de vivado o si el proyecto se ha dañado.

1.5.2 Exploración del proyecto

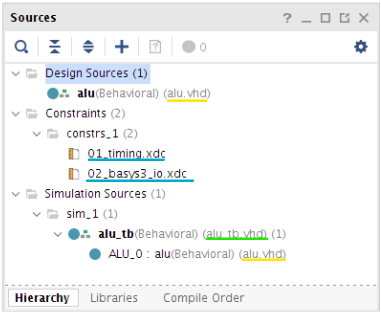

Explora la estructura del proyecto en el panel Sources:

Puedes observar que los archivos VHDL se han clasificado en tres grupos:

- Design Sources:

Contiene los archivos VHDL que describen el módulo alu. Modelan el hardware que se implementará en la FPGA.

- Simulation Sources:

Contiene los archivos VHDL que se utilizan en simulación: el banco de pruebas alu_tb y el módulo alu. Fíjate que la forma de organizar los módulos reproduce la jerarquía utilizada, y que el archivo alu.vhd aparece en ambos grupos.

- Constraints:

Contiene los archivos

01_timing.xdcy02_basys3_io.xdccon las restricciones de temporización y localización de pines que se aplicarán al diseño.

Puedes abrir los archivos y editarlos haciendo doble clic sobre ellos en el panel Sources. Desde este panel puedes añadir o eliminar archivos del proyecto, así como crear nuevos archivos VHDL o de restricciones.

Recuerda que los archivos

de código fuente deben situarse en la carpeta ./rtl, los testbenches en la

carpeta ./sim y las restricciones en la carpeta ./constraints.