2.3 Plan de pruebas (simulación)

Objetivo:

Verificar la funcionalidad del módulo VHDL lab2 dando valor a sus entradas y

observando sus salidas bajo distintas condiciones.

Casos de Prueba:

En todos los casos debe verificarse que las señales internas;

producto,abs_prod,mill_sgn,bcd,bcd_digitoySSse calculan correctamente.

Prueba de Propagación de Señales:

T1 Verificar los casos en los que la salida SS toma los números del 0 al 9

T2 Verificar que la salida SS representa de forma correcta el signo

-

Prueba de Valores Límite:

T3.1: Comprobar que el producto de 31*31 = 961 se representa correctamente en BCD y en 7 segmentos.

T3.2: Comprobar que el producto de -32*31 = -992 se representa correctamente en BCD y en 7 segmentos.

T3.3: Comprobar que el producto de 31*-32 = -992 se representa correctamente en BCD y en 7 segmentos.

T3.4: Comprobar que el producto de -32*-32 = 1024 se representa correctamente en BCD y en 7 segmentos.

Pruebas adicionales:

T4 Añade otros test que consideres necesarios para verificar el correcto funcionamiento del diseño.

Este plan de pruebas asegura que el módulo VHDL lab2 se prueba exhaustivamente

para varios escenarios y casos extremos.

testbench.

En el archivo de recursos encontrarás un banco de pruebas (

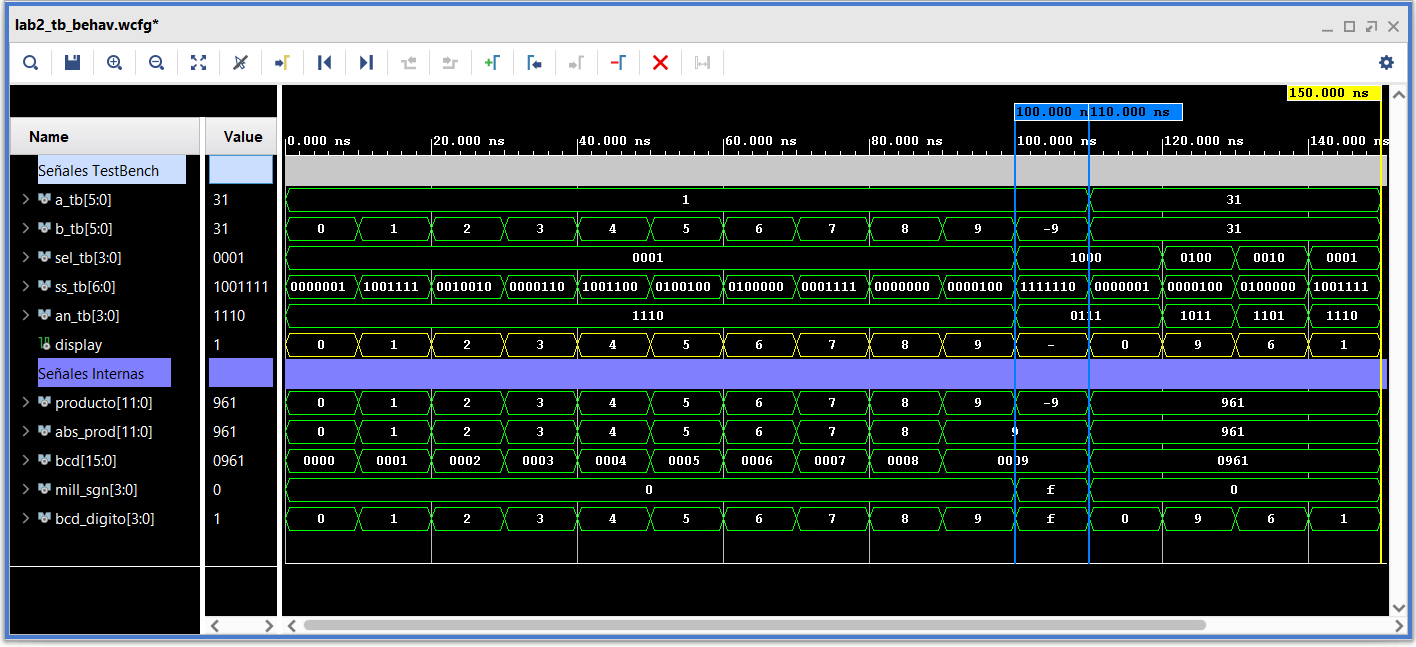

sim/lab2_tb.vhd) que debes completar siguiendo el plan de pruebas descrito anteriormente.Una vez lanzada la simulación, añade las señales internas

producto,abs_prod,mill_sgn,bcd,bcd_digitoySSa la ventana de formas de onda y guarda la configuración.Pon breakpoints en los puntos indicados en el código para detener la simulación y comprobar los valores de las señales en cada test. Para activar un breakpoint, haz clic en el círculo \(\textcolor{red}{◯}\) situado en el margen izquierdo de la línea deseada en el editor de Vivado.

Reinicia las simulación

y avanza hasta el siguiente breakpoint

Código VHDL.

1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 5 entity lab2_tb is 6 end entity lab2_tb; 7 8 architecture Behavioral of lab2_tb is 9 signal a_tb : signed(5 downto 0); 10 signal b_tb : signed(5 downto 0); 11 signal sel_tb : std_logic_vector(3 downto 0); 12 signal ss_tb : std_logic_vector(6 downto 0); 13 signal an_tb : std_logic_vector(3 downto 0); 14 15 signal display: character; -- Número mostrado en el display 16 17 component lab2 18 port ( 19 A : in std_logic_vector(5 downto 0); 20 B : in std_logic_vector(5 downto 0); 21 SEL : in std_logic_vector(3 downto 0); 22 SS : out std_logic_vector(6 downto 0); 23 AN : out std_logic_vector(3 downto 0) 24 ); 25 end component; 26 27 begin 28 -- Instanciar el módulo bajo prueba 29 uut: lab2 30 port map ( 31 A => std_logic_vector(a_tb), 32 B => std_logic_vector(b_tb), 33 SEL => sel_tb, 34 SS => ss_tb, 35 AN => an_tb 36 ); 37 38 -- Proceso de Prueba 39 process 40 begin 41 -- Verificar en todos los tests que las señales internas `producto`, 42 -- `abs_prod`, `mill_sgn`, `bcd `, `bcd_digito` y `SS` se calculan y 43 -- se propagan correctamente.` 44 -- T1 Verificar los casos en los que la salida SS toma los números del 0 al 9. 45 -- ponemos A=1, B=0..9, y seleccionamos las unidades. 46 sel_tb <= "0001"; -- Selección dígito unidades 47 a_tb <= to_signed(1,6); -- Fijar A=1 48 for i in 0 to 9 loop 49 b_tb <= to_signed(i,6); -- B=0..9 50 wait for 10 ns; -- Esperar a que se propague 51 end loop; 52 wait for 0 ns; 53 -- >>> Pon un breakpoint en la línea anterior y Comprueba T1 54 55 -- T2 Verificar que la salida SS representa de forma correcta el signo `-` 56 b_tb <= to_signed(-9,6); -- Fijar B=-9 57 sel_tb <= "1000"; -- Selección dígito signo 58 wait for 10 ns; -- Esperar a que se propague 59 wait for 0 ns; 60 -- >>> Pon un breakpoint en la línea anterior y Comprueba T2 61 62 -- T3: Valores Límite. Comprobar que los productos: 31*31, -32*31, 31*-32 y -32*-32 63 -- se representan correctamente en BCD y en 7 segmentos. 64 --- T3.1: 31*31 = 961 65 a_tb <= to_signed(31,6); -- Fijar A=31 66 b_tb <= to_signed(31,6); -- Fijar B=31 67 sel_tb <= "1000"; -- Selección dígito signo/millares 68 wait for 10 ns; -- Esperar a que se propague 69 sel_tb <= "0100"; -- Selección dígito signo/millares 70 wait for 10 ns; -- Esperar a que se propague 71 sel_tb <= "0010"; -- Selección dígito signo/millares 72 wait for 10 ns; -- Esperar a que se propague 73 sel_tb <= "0001"; -- Selección dígito signo/millares 74 wait for 10 ns; -- Esperar a que se propague 75 wait for 0 ns; 76 -- >>> Pon un breakpoint en la línea anterior y Comprueba T3.1 77 78 -- Escribe el código paro los otros tres tests: 79 -- T3.2: -32*31 = -992 80 -- T3.3: 31*-32 = -992 81 -- T3.4: -32*-32 = 1024 82 83 -- T4: Añade otros test que consideres necesarios para verificar el correcto 84 -- funcionamiento del diseño. 85 86 wait; 87 end process; 88 89 -- Número mostrado en el display en función del valor de ss_tb 90 -- abcdefg 91 display <= '0' when ss_tb = "0000001" else 92 '1' when ss_tb = "1001111" else 93 '2' when ss_tb = "0010010" else 94 '3' when ss_tb = "0000110" else 95 '4' when ss_tb = "1001100" else 96 '5' when ss_tb = "0100100" else 97 '6' when ss_tb = "0100000" else 98 '7' when ss_tb = "0001101" else 99 '8' when ss_tb = "0000000" else 100 '9' when ss_tb = "0000100" else 101 '-' when ss_tb = "1111110" else 102 ' ' when ss_tb = "1111111" else 103 '?'; 104 105 end architecture Behavioral;

Resultados Esperados:

Al finalizar la simulación, los resultados esperados en cada test son:

T1: La salida SS debe mostrar los números del 0 al 9 correctamente en el display, si hubiera algún código no admitido mostraría el caracter \(\textsf{'?'}\).

T2: La salida SS debe mostrar el signo \(\textsf{'-'}\) correctamente en el display.

T3.1: La salida SS debe mostrar 961 correctamente en BCD y en 7 segmentos.

T3.2: La salida SS debe mostrar -992 correctamente en BCD y en 7 segmentos.

T3.3: La salida SS debe mostrar -992 correctamente en BCD y en 7 segmentos.

T3.4: La salida SS debe mostrar 1024 correctamente en BCD y en 7 segmentos.

T4: Los resultados dependerán de los tests adicionales que se hayan implementado.

Asegúrate de que todas las señales internas se comportan según lo esperado durante cada prueba.