3.3 Plan de pruebas (simulación)

3.3.1 Objetivo:

Verificar la funcionalidad del módulo VHDL uart_tx dando valor a sus entradas y

observando sus salidas bajo distintas condiciones.

uart_tx, es un transmisor UART que implementa:

Sincronización de entrada (anti-metaestabilidad con 2 flip-flops)

Filtro de rebotes (debouncing) del pulsador (muestreo cada 5 ms)

Detección de flancos de subida

Transmisión serie con formato: START (0) + 8 DATA (LSB primero) + STOP (1)

Velocidad: 19200 baud @ 100 MHz (5208 ciclos por bit)

El testbench incluye un proceso de reconstrucción de trama que:

Detecta el bit de START (falling edge de TX)

Muestrea los 8 bits de datos en el centro de cada período de bit

Verifica el bit de STOP

Genera señal

tx_reconstruidocon el dato recibido (o “X” si hay error)

3.3.2 Configuración de Prueba

3.3.2.1 Parámetros de Simulación

Constante |

Valor |

Descripción |

|---|---|---|

|

10 ns |

Período del reloj (100 MHz) |

|

1 sec / 19200 ≈ 52.08 μs |

Duración de cada bit UART |

|

5 ms |

Período de muestreo del debouncing |

|

10 × 52.08 μs ≈ 520.8 μs |

Duración total de una trama (10 bits) |

3.3.2.2 Señales del Testbench

Entradas al DUT :

rst_tb: Reset asíncrono activo en altoclk_tb: Reloj de 100 MHz (generado automáticamente)sw_tb: Datos de 8 bits a transmitirbtnd_tb: Señal de botón (con patrones de pulsación)

Salidas del DUT :

tx_tb: Línea de transmisión UART

Señales de verificación:

dtxaux: Vector auxiliar interno para reconstruir bitstx_reconstruido: Dato reconstruido de la trama (8 bits)

3.3.3 Casos de Prueba Implementados

3.3.3.1 Test 1: Reset y Condiciones Iniciales

- Propósito:

Verificar que el módulo se inicializa correctamente tras un reset

- Código implementado:

rst_tb <= '1'; -- activa reset wait for 5 * C_CLK_PERIOD; rst_tb <= '0'; -- desactiva reset wait for 5 * C_CLK_PERIOD; wait for 0 ns; -- Delta delay

- Verificaciones esperadas:

TX = '1'(línea en IDLE)Registro de desplazamiento interno en estado inicial

Temporizadores iniciados,

- Resultado esperado:

Sistema listo para primera transmisión

3.3.3.2 Pruebas de Transmisión de Patrones

Tests 2-5 verifican la transmisión correcta de distintos patrones de datos.

Estructura común a todos los tests:

sw_tb <= x"XX"; -- Patrón a transmitir

btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; -- Patrón de la pulsación

wait for 2 * C_DEBOUNCE_TIME + 2 ms; -- Periodo de la pulsación (>> tiempo de transmisión)

Parámetros y resultados esperados por test:

Test |

Patrón |

Bits de datos (LSB primero) |

Verificación |

|---|---|---|---|

Test 2 |

|

1-0-1-0-1-0-1-0 |

|

Test 3 |

|

0-1-0-1-0-1-0-1 |

|

Test 4 |

|

0-0-0-0-0-0-0-0 |

|

Test 5 |

|

1-1-1-1-1-1-1-1 |

|

Verificaciones esperadas para todos los tests (2-5):

Bit START = “0” (primer bit transmitido)

8 bits de datos transmitidos en orden correcto (LSB primero)

Bit STOP = “1” (último bit)

Valor

tx_reconstruidocoincide con el patrón cargado enSWDuración total de trama ≈ 520.8 μs

Cada bit dura exactamente 5208 ciclos de reloj (52.08 μs)

Resultado esperado para todos: Trama UART correcta con patrones transmitidos sin errores

3.3.3.3 Test 6: Verificación de Debouncing

- Propósito:

Verificar que el circuito de debouncing elimina rebotes y glitches.

- Código implementado:

sw_tb <= x"99"; btnd_tb <= '0', '1' after C_DEBOUNCE_TIME, '0' after C_DEBOUNCE_TIME + 400 * C_CLK_PERIOD, '1' after C_DEBOUNCE_TIME + 1000 * C_CLK_PERIOD, '0' after C_DEBOUNCE_TIME + 2000 * C_CLK_PERIOD, '1' after C_DEBOUNCE_TIME + 4000 * C_CLK_PERIOD, '0' after C_DEBOUNCE_TIME + 7000 * C_CLK_PERIOD, '1' after C_DEBOUNCE_TIME + 10000 * C_CLK_PERIOD; wait for 2 * C_DEBOUNCE_TIME + 2 ms;

- Verificaciones esperadas:

Glitches cortos (400, 1000 ciclos) NO disparan transmisión

Solo el pulso final estable (> 5 ms) es reconocido

Se transmite una sola trama con 0x99

tx_reconstruido = 0x99

Contador de debouncing filtra correctamente

- Resultado esperado:

Debouncing funcional, inmune a rebotes

3.3.3.4 Test 7: Reset Durante Transmisión

- Propósito:

Verificar comportamiento ante reset asíncrono durante una transmisión activa

- Código implementado:

sw_tb <= x"77"; btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; wait until tx_tb = '0'; -- Espera bit de START wait for 0.25 * C_BIT_TIME; -- Avanza 1/4 de bit rst_tb <= '1'; -- Activa reset wait for 3 * C_CLK_PERIOD; rst_tb <= '0'; -- Libera reset wait for C_DEBOUNCE_TIME;

- Verificaciones esperadas:

Transmisión de 0x77 se interrumpe inmediatamente

TXvuelve a “1” (IDLE) tras resetRegistro de desplazamiento se reinicia a estado inicial

tx_reconstruidomarcará error (“X”) por trama incompletaSistema queda listo para nueva transmisión

- Resultado esperado:

Reset asíncrono recupera el sistema correctamente

3.3.3.5 Test 8: Transmisión Final

- Propósito:

Verificar operación normal tras tests previos, incluyendo reset

- Código implementado:

sw_tb <= x"EA"; btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; wait for 2 * C_DEBOUNCE_TIME + 2 ms;

- Verificaciones esperadas:

START = “0”

Datos: 0-1-0-1-0-1-1-1 (LSB primero: 0xEA)

STOP = “1”

tx_reconstruido = 0xEASistema funcional tras tests anteriores

- Resultado esperado:

Operación normal verificada

testbench.

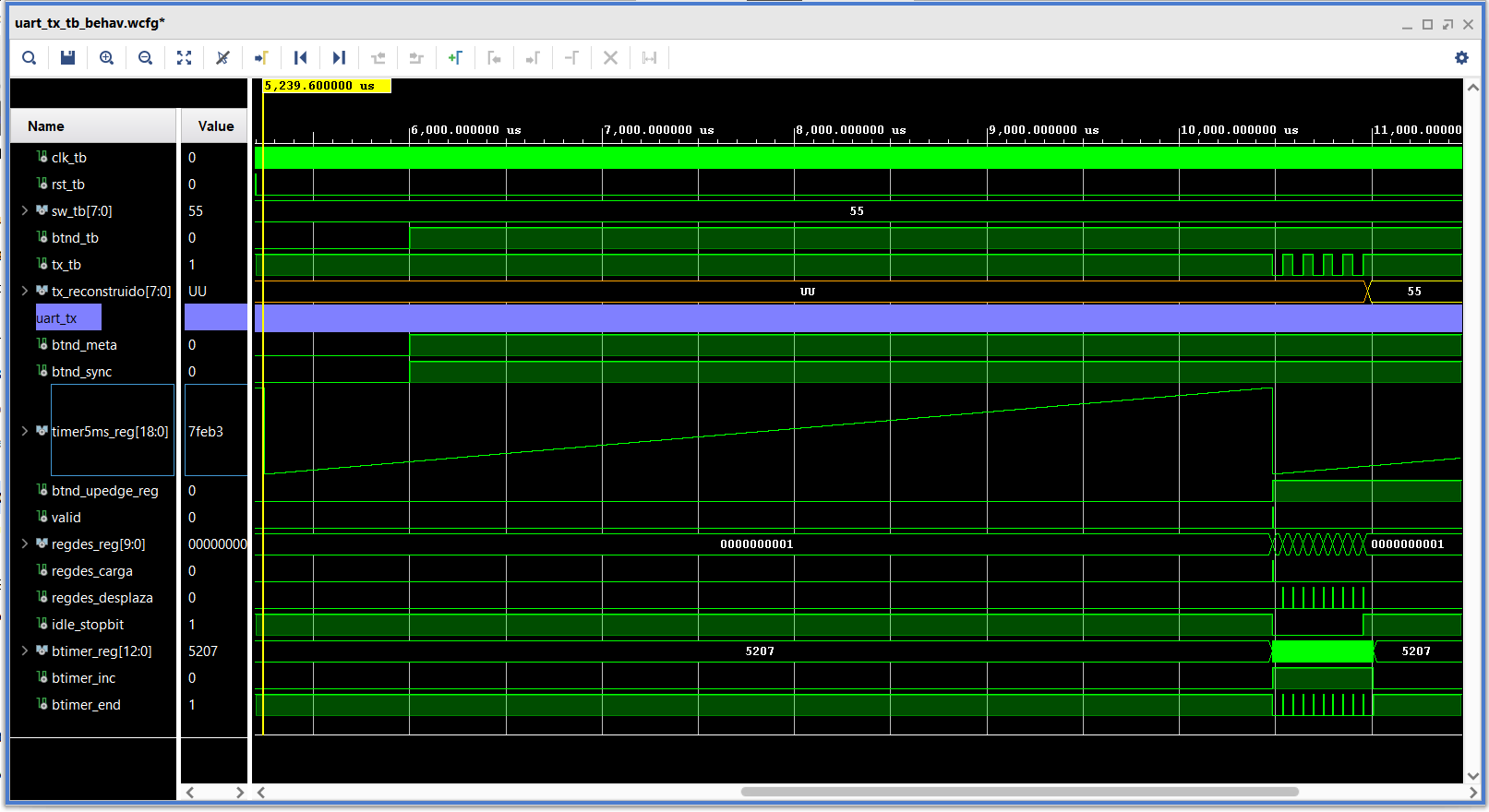

En el archivo de recursos encontrarás un banco de pruebas (

sim/uart_tx_tb.vhd) que debes completar siguiendo el plan de pruebas descrito anteriormente.Una vez lanzada la simulación, añade las señales internas a la ventana de formas de onda, escoge el radix adecuado para cada una de ellas y guarda la configuración.

Pon breakpoints en los puntos indicados en el código para detener la simulación y comprobar los valores de las señales en cada test.

Reinicia las simulación

y avanza hasta el siguiente breakpoint

Código VHDL.

1library ieee; 2use ieee.std_logic_1164.all; 3use ieee.numeric_std.all; 4 5entity uart_tx_tb is 6end; 7 8architecture Behavioral of uart_tx_tb is 9 -- Declaración de los componentes 10 component uart_tx 11 port ( 12 RST : in std_logic; 13 CLK : in std_logic; 14 SW : in std_logic_vector (7 downto 0); 15 BTND : in std_logic; 16 TX : out std_logic 17 ); 18 end component; 19 20 -- Declaración de constantes 21 -- periodo de la señal de reloj 22 constant C_CLK_PERIOD : time := 10 ns; 23 -- tiempo de bit 24 constant C_BIT_TIME : time := 1 sec/19200; 25 -- tiempo de rebotes 26 constant C_DEBOUNCE_TIME : time := 5 ms; 27 -- tiempo total de una trama UART (1 start + 8 data + 1 stop) 28 constant C_FRAME_TIME : time := 10 * C_BIT_TIME; 29 30 -- Declaración de señales 31 -- señal de reloj 32 signal clk_tb : std_logic := '0'; 33 -- señal de reset 34 signal rst_tb : std_logic := '1'; 35 -- señal de entrada/salida del dispositivo bajo prueba 36 signal sw_tb : std_logic_vector(7 downto 0) := x"55"; -- Valor inicial (puede ser modificado en los casos de test) 37 signal btnd_tb : std_logic := '0'; 38 signal tx_tb : std_logic; 39 -- señales utilizadas para la reconstrucción de la trama transmitida 40 signal dtxaux: std_logic_vector(7 downto 0); -- señal auxiliar para reconstruir la trama 41 signal tx_reconstruido : std_logic_vector(7 downto 0); -- último dato procesado (reconstruido a partir de la trama transmitida) 42begin 43 44 -- instanciación del dispositivo bajo prueba 45 uart_tx_inst : uart_tx 46 port map 47 ( 48 RST => rst_tb, 49 CLK => clk_tb, 50 SW => sw_tb, 51 BTND => btnd_tb, 52 TX => tx_tb 53 ); 54 55 -- Generación de la señal de reloj 56 clk_tb <= not clk_tb after C_CLK_PERIOD / 2; 57 58 -- Reconstrucción del dato presente en la trama transmitida 59 process 60 begin 61 wait until tx_tb = '0'; -- Espera el bit de start 62 wait for C_BIT_TIME/2; -- Espera ½ bit 63 -- bit de start 64 if (tx_tb /= '0') then 65 tx_reconstruido <= (others => 'X'); -- Error, bit de start 66 else 67 -- 8 bits del caracter 68 for i in 0 to 7 loop 69 wait for C_BIT_TIME; -- Espera 1 bit 70 dtxaux(i) <= tx_tb; -- bit i 71 end loop; 72 73 wait for C_BIT_TIME; -- Espera 1 bit 74 -- bit de stop 75 if (tx_tb /= '1') then 76 tx_reconstruido <= (others => 'X'); -- Error, bit de stop 77 else 78 tx_reconstruido <= dtxaux; 79 end if; 80 end if; 81 end process; 82 83 -- Casos de test 84 process 85 begin 86 -- T1: Reset y condiciones iniciales 87 rst_tb <= '1'; -- activa reset 88 wait for 5 * C_CLK_PERIOD; -- duración del pulso de reset 89 rst_tb <= '0'; -- desactiva reset 90 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 91 -- >>> Pon un breakpoint en la línea anterior y Comprueba T1 92 93 -- Test 2: Transmision 0x55 94 sw_tb <= x"55"; -- Dato de entrada 95 -- patron de pulsación: 96 btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; 97 wait for 2 * C_DEBOUNCE_TIME + 2 ms; -- espera fin de pulsacion 98 rst_tb <= '0'; -- desactiva reset 99 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 100 -- >>> Pon un breakpoint en la línea anterior y Comprueba T2 101 102 -- Test 3: Transmision 0xAA 103 sw_tb <= x"AA"; -- Dato de entrada 104 -- patron de pulsación: 105 btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; 106 wait for 2 * C_DEBOUNCE_TIME + 2 ms; -- espera fin de pulsacion 107 rst_tb <= '0'; -- desactiva reset 108 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 109 -- >>> Pon un breakpoint en la línea anterior y Comprueba T3 110 111 -- Test 4: Transmision 0x00 112 sw_tb <= x"00"; -- Dato de entrada 113 -- patron de pulsación: 114 btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; 115 wait for 2 * C_DEBOUNCE_TIME + 2 ms; -- espera fin de pulsacion 116 rst_tb <= '0'; -- desactiva reset 117 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 118 -- >>> Pon un breakpoint en la línea anterior y Comprueba T4 119 120 -- Test 5: Transmision 0xFF 121 sw_tb <= x"FF"; -- Dato de entrada 122 -- patron de pulsación: 123 btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; 124 wait for 2 * C_DEBOUNCE_TIME + 2 ms; -- espera fin de pulsacion 125 rst_tb <= '0'; -- desactiva reset 126 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 127 -- >>> Pon un breakpoint en la línea anterior y Comprueba T5 128 129 -- Test 6: Debouncing 130 sw_tb <= x"99"; -- Dato de entrada 131 -- patron de pulsación: 132 btnd_tb <= '0', 133 '1' after C_DEBOUNCE_TIME, 134 '0' after C_DEBOUNCE_TIME + 400 * C_CLK_PERIOD, 135 '1' after C_DEBOUNCE_TIME + 1000 * C_CLK_PERIOD, 136 '0' after C_DEBOUNCE_TIME + 2000 * C_CLK_PERIOD, 137 '1' after C_DEBOUNCE_TIME + 4000 * C_CLK_PERIOD, 138 '0' after C_DEBOUNCE_TIME + 7000 * C_CLK_PERIOD, 139 '1' after C_DEBOUNCE_TIME + 10000 * C_CLK_PERIOD; 140 wait for 2 * C_DEBOUNCE_TIME + 2 ms; -- espera fin de pulsacion 141 rst_tb <= '0'; -- desactiva reset 142 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 143 -- >>> Pon un breakpoint en la línea anterior y Comprueba T6 144 145 -- Test 7: Reset durante la transmisión 146 sw_tb <= x"77"; -- Dato de entrada 147 -- patron de pulsación: 148 btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; 149 wait until tx_tb = '0'; -- Espera el bit de start 150 151 wait for 0.25 * C_BIT_TIME; 152 rst_tb <= '1'; 153 wait for 3 * C_CLK_PERIOD; 154 rst_tb <= '0'; 155 wait for C_DEBOUNCE_TIME; 156 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 157 -- >>> Pon un breakpoint en la línea anterior y Comprueba T6 158 159 -- Test 8: Transmision 0xEA 160 sw_tb <= x"EA"; -- Dato de entrada 161 -- patron de pulsación: 162 btnd_tb <= '0', '1' after C_DEBOUNCE_TIME + 1 ms; 163 wait for 2 * C_DEBOUNCE_TIME + 2 ms; -- espera fin de pulsacion 164 rst_tb <= '0'; -- desactiva reset 165 wait for 0 ns; -- Delta delay: permite que otros procesos ejecuten y propaguen cambios 166 -- >>> Pon un breakpoint en la línea anterior y Comprueba T5 167 168 wait; 169 170 end process; 171 172 173end architecture Behavioral;Resultados Esperados:

Se considera un test pasado si para cada test se cumple:

Formato de trama correcto:

Bit START = “0” (primer bit transmitido)

8 bits de datos en orden correcto (LSB primero)

Bit STOP = “1” (último bit)

Timing preciso:

Cada bit dura exactamente 5208 ciclos de reloj

Período de bit = 52.08 μs

Trama completa = 520.8 μs

Validación automática:

tx_reconstruidocoincide consw_tbNo hay valores “X” en

tx_reconstruido(excepto Test 7)Debouncing funcional:

Glitches < 5 ms son ignorados (Test 6)

Pulsaciones > 5 ms disparan transmisión

Robustez:

Reset durante transmisión recupera el sistema (Test 7)

TX retorna a “1” (IDLE) tras reset

Se considera un test fallido si:

tx_reconstruido≠sw_tben tests normales (T2-T6, T8)Bit START ≠ “0” o bit STOP ≠ “1”

Duración de bit fuera de especificación (> ±2% de 52.08 μs)

Transmisión espontánea sin pulsar botón

Falso positivo: glitches < 5 ms disparan transmisión (Test 6)

Falso negativo: pulsación > 5 ms no dispara transmisión

Sistema no recupera tras reset (Test 7)