3.4 Síntesis e implementación

A continuación se realizan los procesos de síntesis lógica e implementación. Se utilizan los ficheros de restricciones incluidos en el proyecto:

Fichero de restricciones temporales:

constraints/01_timing.xdc1 # -------------------------------------------------------------------------------- 2 # Archivo: 01_timing.xdc 3 # Descripción: Restricciones de temporización para diseño UART asíncrono TX 4 # -------------------------------------------------------------------------------- 5 6 # 1. Definición del Reloj Principal "sys_clk" conectado al pin CLK 7 # -------------------------------------------------------------------------------- 8 # Se define el reloj principal del sistema con una frecuencia de 100 MHz. 9 # Este comando establece la referencia base para todo el análisis de timing interno. 10 # Periodo: 10ns | Duty Cycle: 50% 11 create_clock -add -name sys_clk -period 10.00 -waveform {0 5} [get_ports CLK] 12 13 14 # 2. Entradas Asíncronas (Switches, Pulsadores y Reset) 15 # -------------------------------------------------------------------------------- 16 # Las señales SW, BTND y RST son asíncronas: no tienen una relación de fase fija 17 # con el reloj del sistema y su cambio depende de la interacción humana. 18 # 19 # Se aplica 'set_false_path' para indicar a Vivado que no intente cumplir tiempos 20 # de setup/hold en estos puertos, ya que físicamente es imposible garantizarlos. 21 set_false_path -from [get_ports {SW[*] BTND RST}] 22 23 24 # 3. Sincronización y Prevención de Metaestabilidad 25 # -------------------------------------------------------------------------------- 26 # Para evitar fallos por metaestabilidad al leer señales externas (como BTND), 27 # se utiliza una cadena de registros (sincronizador). 28 # 29 # Restringimos el camino hacia el primer registro (btnd_meta_reg) como 'false_path' 30 # para que el analizador de tiempos ignore las violaciones en ese nodo específico. 31 32 set_false_path -to [get_cells btnd_meta_reg] 33 34 # 4. Interfaz Serie UART (Salida TX) 35 # -------------------------------------------------------------------------------- 36 # La señal TX pertenece a un protocolo de comunicación asíncrono. Dado que el 37 # receptor externo utiliza su propio reloj independiente para muestrear los datos, 38 # no existe una relación de tiempo síncrona con nuestro reloj interno. 39 # 40 # Declaramos 'false_path' para liberar al compilador de optimizaciones innecesarias 41 # en esta señal de baja velocidad. 42 set_false_path -to [get_ports TX] 43 44 # 5. Configuración de sincronización: Pulsador (btnd) 45 # ASYNC_REG identifica registros de sincronización para maximizar el MTBF (tiempo entre fallos), 46 # forzando su proximidad física y desactivando optimizaciones lógicas (retiming) que 47 # podrían comprometer la resolución de metaestabilidad. 48 set_property ASYNC_REG TRUE [get_cells {*_meta_* *_sync_*}]Fichero de restricciones de localización:

constraints/02_basys3_io.xdcDebe ser completado por el usuario indicando la localización de cada puerto. Los nombres de los pines puedes obtenerlos del manual de usuario de la placa Basys 3.

Una vez completados los ficheros de restricciones, se ejecutan los procesos de síntesis e implementación, en Flow Navigator en Vivado:

.

.

Análisis de resultados de implementación

Sobre los ficheros de restricciones:

En el fichero de restricciones temporales se ha declarado una restricción de reloj, comando xdc

create_clock.En la consola tcl de vivado ejecuta el comando

help create_clockpara obtener información sobre su sintaxis y significado de cada parámetro. A continuación, responde a las siguientes preguntas:¿Cuál es la frecuencia del reloj definido en la restricción?

¿Cuál es el periodo del reloj definido en la restricción?

¿Cuál es el duty cycle del reloj definido en la restricción?

¿Qué pin de la FPGA está conectado a este reloj?

En este se incluye además una restricción de sincronización para el pulsador BTND, utilizando el comando

set_property ASYNC_REG TRUE. Investiga el significado de esta propiedad y responde a las siguientes preguntas:¿Cuál es el propósito de la propiedad ASYNC_REG en Vivado?

¿Cómo afecta esta propiedad a la síntesis e implementación del diseño?

¿Por qué es importante para maximizar el MTBF (Mean Time Between Failures) del sistema?

Tras realizar con éxito el proceso síntesis e implementación:

Utiliza los comandos

report_utilizationyreport_timing, para obtener los siguientes datos:Recursos hardware utilizados:

Slice LUTs:

Slice Registers:

Bonded IOBs:

- Tiempo máximo de propagación: ____ ns, correspondiente al camino crítico

entre los puertos ____ y ____.

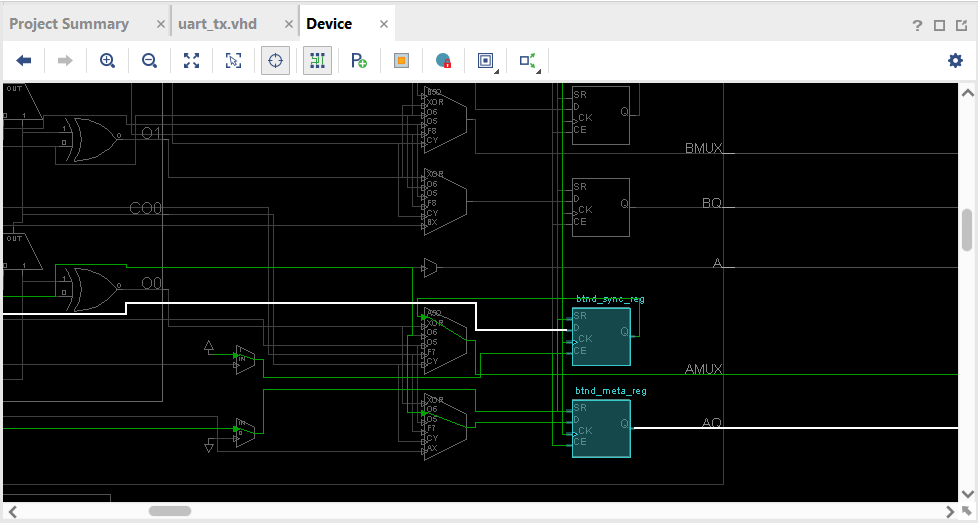

Verifica que los dos biestables del sincronizador del pulsador (btnd_meta_reg y btnd_sync_reg) están colocados físicamente cerca uno del otro.

Para ello, ejecuta el siguiente comando tcl en la consola de Vivado:

select_objects [get_cells -hierarchical -filter {NAME =~ *_meta_* || NAME =~ *_sync_*}]En la pestaña «Device» de vivado se mostrarán los registros seleccionados, haz clic en Autofit Selection para ajustar la vista a los registros seleccionados.

Verifica que están situados en la misma región de la FPGA (por ejemplo, ambos en la región «SLICE_X0Y0» o «SLICE_X1Y0», etc.) y que no hay otros registros intercalados entre ellos. Esto confirmará que se han colocado físicamente juntos para maximizar el MTBF del sincronizador.