4.3 Plan de pruebas (simulación)

4.3.1 Objetivo:

Verificar la funcionalidad del módulo VHDL uart_rx dando valor a sus entradas y

observando sus salidas bajo distintas condiciones.

uart_rx, es un receptor UART que implementa:

Sincronización de entrada (anti-metaestabilidad con 2 flip-flops)

Recepción serie con formato: START (0) + 8 DATA (LSB primero) + STOP (1)

Velocidad: 19200 baud @ 100 MHz (5208 ciclos por bit)

Visualización del dato recibido en LEDs y display 7 segmentos

Indicador de recepción de datos (DRI)

4.3.2 Configuración de Prueba

4.3.2.1 Parámetros de Simulación

Constante |

Valor |

Descripción |

|---|---|---|

|

10 ns |

Periodo del reloj (100 MHz) |

|

1 sec / 19200 |

Duración de cada bit UART (19200 baudios) |

4.3.2.2 Señales del Testbench

Entradas al DUT :

clk_tb: Reloj de 100 MHz (generado automáticamente)rst_tb: Reset asíncrono activo en altorx_tb: Línea serie emulada

Salidas del DUT :

dato_tb: Dato recibido (8 bits) mostrado en los LEDsss_tb: Segmentos del display 7 segmentosan_tb: Ánodos del display para multiplexacióndri_tb: Indicador de recepción de dato (activo durante la recepción de la trama)

Señales de verificación:

rx_byte: Dato a recibir (emulador línea serie)rx_sequence: Secuencia de caracteres ASCII para test consecutivonumero: Carácter visualizado en el display 7 segmentos

4.3.3 Casos de Prueba Implementados

4.3.3.1 Test 1: Reset y Condiciones Iniciales

- Propósito:

Verificar que el módulo se inicializa correctamente tras un reset

- Código implementado:

rst_tb <= '1', '0' after 35 ns; wait for 40 ns; wait for 0 ns;

- Verificaciones esperadas:

DRI = '0'(no hay recepción de dato)Registro de desplazamiento en estado inicial

Temporizador inicializado a 0

Contador de bits en 0

Máquina de estados en estado

sinc0(sincronización)

- Resultado esperado:

Sistema listo para recibir primera trama

4.3.3.2 Test 2: Sincronización de RX

- Propósito:

Verificar que el sincronizador de dos etapas funciona correctamente.

- Código implementado:

rx_tb <= '1', '0' after 5 * clk_period, '1' after 15 * clk_period; wait for 20 * clk_period; wait for 0 ns;

- Verificaciones esperadas:

Retardo de sincronización de 2 ciclos de reloj

Señal sincronizada correcta

- Resultado esperado:

Sincronizador funcional.

4.3.3.3 Pruebas de Recepción de Patrones

Tests 3-5 verifican la recepción correcta de distintos patrones de datos.

Estructura común a todos los tests:

rx_byte <= x"XX"; -- byte a recibir

rx_tb <= '0'; -- Bit de start

for i in 0 to 7 loop -- Iteración por cada bit de dato

wait for BIT_time; -- Espera tiempo de 1 bit

rx_tb <= rx_byte(i); -- Transmite el bit (LSB primero)

end loop;

wait for BIT_time;

rx_tb <= '1'; -- Bit de stop

wait for BIT_time;

wait for 4 * clk_period;

wait for 0 ns;

Parámetros y resultados esperados por test:

Test |

Byte |

Trama (LSB primero) |

Verificación |

|---|---|---|---|

Test 3 |

|

\(\textcolor{blue}{\textsf{0}}\textsf{-1-0-1-0-1-0-1-0-}\textcolor{blue}{\textsf{1}}\) |

|

Verificaciones esperadas para todos los tests (3-5):

Bit START = “0” (primer bit recibido)

8 bits de datos recibidos en orden correcto (LSB primero)

Bit STOP = “1” (último bit validado)

Valor

dato_tbcoincide con el patrón transmitidoDuración total de trama ≈ 10 * BIT_time

Transfer de registro de desplazamiento a registro de salida al finalizar la trama válida

Señal

DRIse activa mientras se recibe la trama.

- Resultado esperado:

Tramas UART recibidas correcta.

4.3.3.4 Test 4.1: Detección de Error - Glitch en Start

- Propósito:

Verificar que el receptor rechaza pulsos cortos (glitches) que no corresponden a bits de start válidos.

- Código implementado:

rst_tb <= '1', '0' after 35 ns; -- Activa reset rx_tb <= '1', '0' after 5 * clk_period, '1' after 25 * clk_period; -- Glitch de 20 ciclos de reloj wait for 30 * clk_period; wait for 0 ns;

- Verificaciones esperadas:

Glitch de 20 ciclos de reloj NO dispara recepción

Máquina de estados rechaza el pulso corto

No se modifica el registro de desplazamiento

Sistema permanece en estado de reposo/sincronización

- Resultado esperado:

Rechazo correcto de glitches cortos

4.3.3.5 Test 4.2: Detección de Error - Bit de Stop Incorrecto

- Propósito:

Verificar que el receptor detecta y rechaza tramas con bit de stop incorrecto (error de trama).

- Código implementado:

rx_byte <= x"50"; -- Dato a transmitir rx_tb <= '0'; -- Bit de start for i in 0 to 7 loop -- Iteracion por cada bit de dato wait for BIT_time; -- Espera tiempo de 1 bit rx_tb <= rx_byte(i); -- Transmite el bit LSB primero end loop; wait for BIT_time; rx_tb <= '0'; -- Bit de stop incorrecto (deberia ser '1') wait for BIT_time; rx_tb <= '1'; wait for 4 * clk_period; wait for 0 ns;

- Verificaciones esperadas:

Detección del error de bit de stop

Máquina de estados vuelve a estado

sinc0Registro de salida NO se actualiza

Display mantiene valor anterior (no 0x50)

Sistema preparado para recibir siguiente trama válida

- Resultado esperado:

Detección de error de framing, rechazo de trama errónea

4.3.3.6 Test 5: Recepción de Datos Consecutivos

- Propósito:

Verificar que el receptor puede manejar múltiples caracteres transmitidos de forma consecutiva sin pérdida de datos ni sincronización.

- Código implementado:

for j in rx_sequence'range loop rx_byte <= rx_sequence(j); rx_tb <= '0'; -- Bit de start for i in 0 to 7 loop -- Iteracion por cada bit de dato wait for BIT_time; -- Espera tiempo de 1 bit rx_tb <= rx_byte(i); -- Transmite el bit LSB primero end loop; wait for BIT_time; rx_tb <= '1'; -- Bit de stop wait for BIT_time; -- Tiempo entre caracteres end loop; wait for 0 ns;

- Secuencia transmitida:

Caracteres ASCII: \(\textsf{"0123456789 "}\) (dígitos 0-9 y espacio) .. code-block:

* '0' (0x30), '1' (0x31), '2' (0x32), '3' (0x33), '4' (0x34) * '5' (0x35), '6' (0x36), '7' (0x37), '8' (0x38), '9' (0x39) * ' ' (0x20) - Espacio

- Verificaciones esperadas:

Recepción correcta de cada carácter consecutivo

No pérdida de datos entre caracteres

Visualización correcta en display de 7 segmentos para cada dígito

Sincronización mantenida entre caracteres

Señal DRI se activa para cada carácter mientras se recibe

Cada dígito se muestra correctamente en la secuencia

- Resultado esperado:

Recepción de múltiples tramas sin errores acumulativos

testbench.

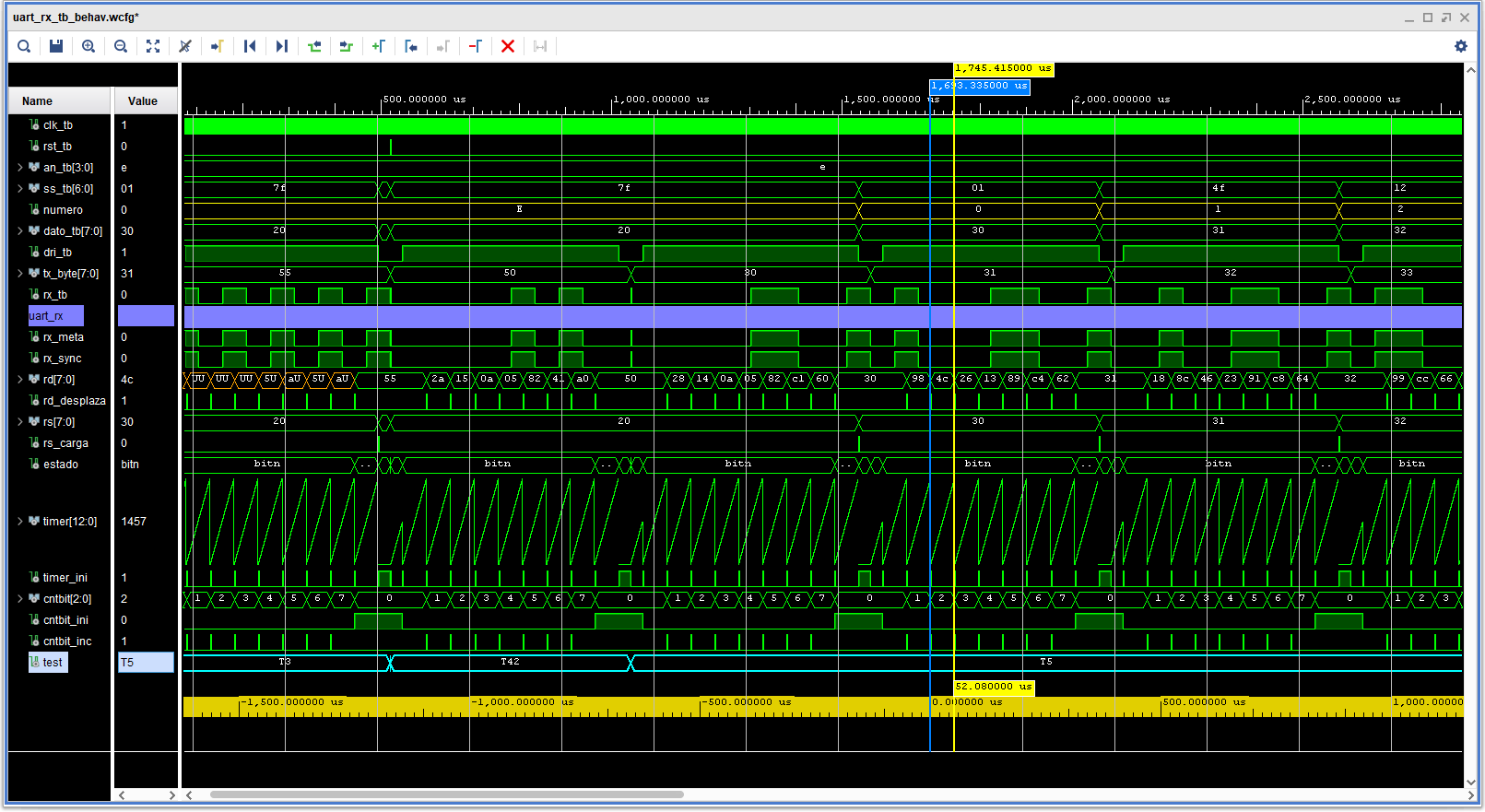

En el archivo de recursos encontrarás un banco de pruebas (

sim/uart_rx_tb.vhd) que verifica la funcionalidad del receptor UART mediante los casos de prueba descritos anteriormente.Una vez lanzada la simulación, añade las señales internas a la ventana de formas de onda. Especialmente las señales:

rx_sync: Señal RX sincronizada con 2 flip-flops

rd: Registro de desplazamiento serie/paralelo

rd_desplaza: Señal de desplazamiento del registro de desplazamiento

rs: Registro de salida con dato almacenado

rs_carga: Señal de carga del registro de salida

estado: Estado actual de la máquina de estados

timer: Contador de ciclos para muestreo central

timer_ini: Señal de inicialización del temporizador

cntbit: Contador de bits recibidos (0-7)

cntbit_inc: Señal de incremento del contador de bits

cntbit_ini: Señal de inicialización del contador de bits

test: Indicador del test actual (T1, T2, T3, T4.1, T4.2, T5)Escoge el radix adecuado para cada señal:

Hexadecimal (

hex) paradato_tb,rsBinario (

bin) parass_tb,rdDecimal (

unsignedounsigned decimal) paratimer,cntbitGuarda la configuración de la ventana de formas de onda.

Pon breakpoints en los puntos indicados en el código (líneas con comentarios

-- >>> Pon un breakpoint en la línea anterior) para detener la simulación y comprobar los valores de las señales en cada test.Reinicia la simulación y avanza hasta el siguiente breakpoint.

Código VHDL del testbench.

1------------------------------------------------------------------------------- 2-- File: uart_rx_tb.vhd 3-- Description: Testbench para el receptor UART (uart_rx) 4-- Verifica la funcionalidad del receptor serie a 19200 baudios 5-- mediante diferentes casos de prueba 6-- Author: 7-- Date: 2025 8-- 9-- Tests: 10-- T1: Reset y condiciones iniciales 11-- T2: Sincronizacion de la senal RX 12-- T3: Recepcion correcta de un dato 13-- T4: Verificacion de errores (glitch en start, error en stop) 14-- T5: Recepcion de rx_sequence consecutivos 15------------------------------------------------------------------------------- 16 17library ieee; 18use ieee.std_logic_1164.all; 19use ieee.numeric_std.all; 20 21entity uart_rx_tb is 22end; 23 24architecture Behavioral of uart_rx_tb is 25 --------------------------------------------------------------------------- 26 -- DECLARACION DEL COMPONENTE BAJO PRUEBA (DUT) 27 --------------------------------------------------------------------------- 28 component uart_rx 29 port ( 30 CLK : in std_logic; -- Reloj del sistema (100 MHz) 31 RST : in std_logic; -- Reset asincrono activo alto 32 RX : in std_logic; -- Linea de recepcion serie 33 DATO : out std_logic_vector (7 downto 0);-- Dato recibido 34 SS : out std_logic_vector (6 downto 0);-- Display 7 segmentos 35 AN : out std_logic_vector (3 downto 0);-- Anodos del display 36 DRI : out std_logic -- Dato Recibido e Indicador de listo 37 ); 38 end component; 39 40 --------------------------------------------------------------------------- 41 -- CONSTANTES DE SIMULACION 42 --------------------------------------------------------------------------- 43 constant clk_period : time := 10 ns; -- Periodo de reloj (100 MHz) 44 constant BIT_time : time := 1 sec/19200; -- Tiempo de bit UART (19200 baudios) 45 46 --------------------------------------------------------------------------- 47 -- SENALES DEL TESTBENCH 48 --------------------------------------------------------------------------- 49 -- Senales conectadas al DUT 50 signal clk_tb : std_logic := '0'; -- Reloj de prueba 51 signal rst_tb : std_logic; -- Reset de prueba 52 signal rx_tb : std_logic; -- Linea RX emulada 53 signal an_tb : std_logic_vector (3 downto 0); -- Anodos 54 signal ss_tb : std_logic_vector (6 downto 0); -- 7 segmentos 55 signal dato_tb : std_logic_vector (7 downto 0); -- Dato recibido 56 signal dri_tb : std_logic; -- Indicador listo 57 58 -- Senales del emulador de transmisor serie 59 signal numero : character; -- Caracter visualizado en 7 segmentos 60 type rx_sequence_t is array (0 to 10) of unsigned(7 downto 0); 61 signal rx_sequence : rx_sequence_t := (x"30", x"31", x"32", x"33", x"34", 62 x"35", x"36", x"37", x"38", x"39", x"20"); 63 signal rx_byte : unsigned(7 downto 0); -- Byte a transmitir en el test 64 65 -- Indicador de número de test 66 type test_t is (T1, T2, T3, T41, T42, T5); 67 signal test : test_t := T1; 68 69begin 70 71 --------------------------------------------------------------------------- 72 -- INSTANCIACION DEL DUT (Device Under Test) 73 --------------------------------------------------------------------------- 74 lab4_inst : uart_rx 75 port map 76 ( 77 CLK => clk_tb, 78 RST => rst_tb, 79 RX => rx_tb, 80 DATO => dato_tb, 81 SS => ss_tb, 82 AN => an_tb, 83 DRI => dri_tb 84 ); 85 86 --------------------------------------------------------------------------- 87 -- GENERADOR DE RELOJ 88 --------------------------------------------------------------------------- 89 clk_tb <= not clk_tb after clk_period/2; 90 91 --------------------------------------------------------------------------- 92 -- PROCESO PRINCIPAL DE VERIFICACION FUNCIONAL DEL DUT 93 --------------------------------------------------------------------------- 94 process 95 begin 96 rx_tb <= '0'; 97 98 ----------------------------------------------------------------------- 99 -- T1: Reset y condiciones iniciales 100 ----------------------------------------------------------------------- 101 rst_tb <= '1', 102 '0' after 35 ns; 103 wait for 40 ns; 104 wait for 0 ns; 105 -- >>> Pon un breakpoint en la linea anterior y Comprueba T1.1 .. T1.7 106 107 ----------------------------------------------------------------------- 108 -- T2: Sincronizacion de RX 109 ----------------------------------------------------------------------- 110 test <= T2; 111 rx_tb <= '1', 112 '0' after 5 * clk_period, 113 '1' after 15 * clk_period; 114 wait for 20 * clk_period; 115 wait for 0 ns; 116 -- >>> Pon un breakpoint en la linea anterior y Comprueba T2.1 117 118 ----------------------------------------------------------------------- 119 -- T3: Verificar la recepcion correcta de un dato 120 ----------------------------------------------------------------------- 121 test <= T3; 122 rx_byte <= x"55"; -- Dato a transmitir: 'U' (ASCII 0x55) 123 rx_tb <= '0'; -- Bit de start 124 for i in 0 to 7 loop -- Iteracion por cada bit de dato 125 wait for BIT_time; -- Espera tiempo de 1 bit 126 rx_tb <= rx_byte(i); -- Transmite el bit LSB primero 127 end loop; 128 wait for BIT_time; 129 rx_tb <= '1'; -- Bit de stop 130 wait for BIT_time; 131 wait for 4 * clk_period; 132 wait for 0 ns; 133 -- >>> Pon un breakpoint en la linea anterior y Comprueba T3.1 .. T3.9 134 135 ----------------------------------------------------------------------- 136 -- T4: Verificar deteccion de errores en la comunicacion 137 ----------------------------------------------------------------------- 138 -- T4.1: Glitch en bit de start (pulso corto que debe ser rechazado) 139 test <= T41; 140 rst_tb <= '1', '0' after 35 ns; -- Activa reset 141 rx_tb <= '1', 142 '0' after 5 * clk_period, 143 '1' after 25 * clk_period; -- Glitch de 20 ciclos de reloj 144 wait for 30 * clk_period; 145 wait for 0 ns; 146 -- >>> Pon un breakpoint en la linea anterior y Comprueba T4.1 147 148 -- T4.2: Error en bit de stop (debe rechazar la trama) 149 test <= T42; 150 rx_byte <= x"50"; -- Dato a transmitir 151 rx_tb <= '0'; -- Bit de start 152 for i in 0 to 7 loop -- Iteracion por cada bit de dato 153 wait for BIT_time; -- Espera tiempo de 1 bit 154 rx_tb <= rx_byte(i); -- Transmite el bit LSB primero 155 end loop; 156 wait for BIT_time; 157 rx_tb <= '0'; -- Bit de stop incorrecto (deberia ser '1') 158 wait for BIT_time; 159 rx_tb <= '1'; 160 wait for 4 * clk_period; 161 wait for 0 ns; 162 -- >>> Pon un breakpoint en la linea anterior y Comprueba T4.2 163 164 ----------------------------------------------------------------------- 165 -- T5: Verificar la recepcion de rx_sequence consecutivos 166 -- Transmite la secuencia: "0123456789 " (digitos y espacio) 167 ----------------------------------------------------------------------- 168 test <= T5; 169 rx_tb <= '1'; 170 for j in rx_sequence'range loop 171 rx_byte <= rx_sequence(j); 172 rx_tb <= '0'; -- Bit de start 173 for i in 0 to 7 loop -- Iteracion por cada bit de dato 174 wait for BIT_time; -- Espera tiempo de 1 bit 175 rx_tb <= rx_byte(i); -- Transmite el bit LSB primero 176 end loop; 177 wait for BIT_time; 178 rx_tb <= '1'; -- Bit de stop 179 wait for BIT_time; -- Tiempo entre caracteres 180 end loop; 181 wait for 0 ns; 182 -- >>> Pon un breakpoint en la linea anterior y Comprueba T5 .. T8 183 -- >>> Utiliza la simulacion completa para verificar T9 184 185 wait; -- Pausa para finalizar el proceso 186 end process; 187 188 --------------------------------------------------------------------------- 189 -- DECODIFICADOR DE 7 SEGMENTOS A CARACTER (para debug) 190 -- Convierte la salida del display a un caracter legible 191 --------------------------------------------------------------------------- 192 numero <= '0' when (ss_tb = "0000001") else -- Digito 0 193 '1' when (ss_tb = "1001111") else -- Digito 1 194 '2' when (ss_tb = "0010010") else -- Digito 2 195 '3' when (ss_tb = "0000110") else -- Digito 3 196 '4' when (ss_tb = "1001100") else -- Digito 4 197 '5' when (ss_tb = "0100100") else -- Digito 5 198 '6' when (ss_tb = "0100000") else -- Digito 6 199 '7' when (ss_tb = "0001101") else -- Digito 7 200 '8' when (ss_tb = "0000000") else -- Digito 8 201 '9' when (ss_tb = "0000100") else -- Digito 9 202 'E'; -- Error/otro caracter 203 204end;