4.4 Síntesis e implementación

A continuación se realizan los procesos de síntesis lógica e implementación. Se utilizan los ficheros de restricciones incluidos en el proyecto:

Fichero de restricciones temporales:

constraints/01_timing.xdcFichero de restricciones de localización:

constraints/02_basys3_io.xdcDebe ser completado por el usuario indicando la localización de cada puerto. Los nombres de los pines puedes obtenerlos del manual de usuario de la placa Basys 3.

Una vez completados los ficheros de restricciones, se ejecutan los procesos de síntesis e implementación, en Flow Navigator en Vivado:

.

.

Análisis de resultados de implementación

Sobre los ficheros de restricciones:

En el fichero de restricciones temporales se ha declarado una restricción de reloj, comando xdc

create_clock, y se han marcado los camino de entrada asíncronos y de salida hacia los visualizadores como «false paths» con el comando xdcset_false_path.En la consola tcl de vivado ejecuta el comando

help set_false_pathpara obtener información sobre su sintaxis y significado. A continuación, responde a las siguientes preguntas:¿Que significa que un camino temporal se marque como «false path»?

¿Por qué es necesario marcar los caminos de entrada asíncronos y de salida hacia los visualizadores como «false paths»?

Tras realizar con éxito el proceso síntesis e implementación:

Utiliza los comandos

report_utilizationyreport_timing, para obtener los siguientes datos:Recursos hardware utilizados:

Slice LUTs:

Slice Registers:

Bonded IOBs:

- Tiempo máximo de propagación: ____ ns, correspondiente al camino crítico

entre los puertos ____ y ____.

Verifica que los dos biestables del sincronizador de la entrad RX (rx_meta_reg y rx_sync_reg) están colocados físicamente cerca uno del otro.

Para ello, ejecuta el siguiente comando tcl en la consola de Vivado:

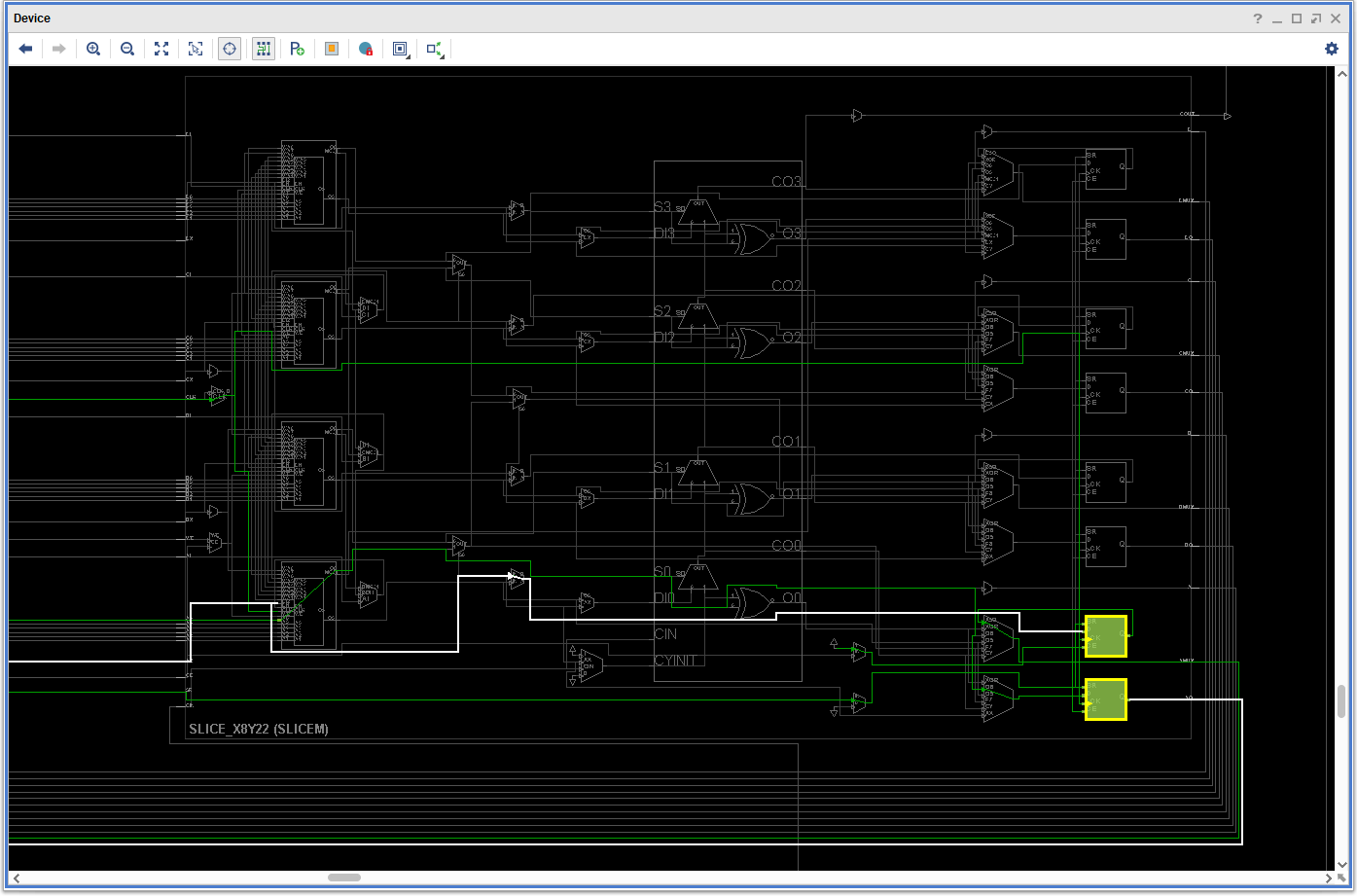

select_objects [get_cells -hierarchical -filter {NAME =~ *_meta_* || NAME =~ *_sync_*}]En la pestaña «Device» de vivado se mostrarán los registros seleccionados, haz clic en Autofit Selection para ajustar la vista a los registros seleccionados.

Verifica que están situados en la misma región de la FPGA (por ejemplo, ambos en la región

"SLICE_X0Y0"o"SLICE_X1Y0", etc.) y que no hay otros registros intercalados entre ellos. Esto confirmará que se han colocado físicamente juntos para maximizar el MTBF del sincronizador.

Los dos biestables del sincronizador situados en SLICE_X8Y22