5.3 Modelado VHDL y verificación

En esta sección se implementarán cada uno de los módulos en VHDL, siguiendo las especificaciones y la arquitectura propuesta. Puedes descargar el archivo de recursos para obtener la estructura de carpetas, las reglas decodificación, y el script para generar el proyecto vivado.

Los ficheros de los módulos sintetizables deben situarse en la carpeta

rtl/.Los ficheros de los testbenches deben situarse en la carpeta

sim/.

Modelado VHDL

Módulo Oscilador: Este módulo implementa el oscilador Levine/Vicanek. Se encargará de generar las muestras de fase (\(I\)) y cuadratura (\(Q\)) en cada ciclo de muestreo.

El diseño debe ser realizado por el estudiante.

Las salidas de las unidades de retardo del oscilador deben tomar los nombres:

si_regysq_reg.

Módulos Adicionales y Herramientas IA: Para los módulos de soporte (UART_TX, Reset Bridge, etc.), utilizaremos el flujo de diseño aumentado con herramientas de IA (

Pro), siguiendo los pasos siguientes:

Especificación → Generación con IA → Auditoría → Simulación → Síntesis

- Especificación:

Define claramente la funcionalidad, interfaz y requisitos de cada módulo (realizado en la sección anterior).

Generación con IA: Utiliza un motor de IA para generar el código VHDL.

Tarea:

El estudiante debe diseñar un prompt efectivo para cada módulo, asegurando que el código generado cumpla con las reglas de estilo y las especificaciones técnicas.

Ejemplo: Para generar el módulo

uart_tx.vhd, comparte con la IA el archivo de reglas de estiloscripts/vhdl_rules.yaml, y prepara un prompt como el siguiente:Actúa como un experto en diseño digital y FPGA, genera el código VHDL y un testbench para una entidad llamada uart_tx. Requerimientos: 1. El diseño debe ser totalmente sintetizable. 2. Utiliza de forma ESTRICTA las reglas de diseño disponibles en vhdl_rules.yaml. 3. Reloj y reset: CLK (100 MHz), RST asíncrono, activo en bajo. 4. Entrada: Interfaz AXI4-Stream (TDATA(8 bits), TVALID, TREADY). 5. Salida: Señal de transmisión UART (TX). 6. Implementar transmisor 230400 bps, formato 8n1. 7. La interfaz de entrada debe ser 100% compatible con AXI4-Stream. 8. Incluye comentarios detallados en español explicando cada proceso. Antes de crear el código VHDL debes explorar distintas opciones de diseño a nivel de arquitectura, y preguntarme cuál modelar en vhdl.

- Nota:

Escribe tu prompt en un documento de texto antes de usarlo para generar el código, te ayudará a refinarlo y mejorar su efectividad.

Guarda el documento con los prompt y adjúntalo a tu entrega para que el profesor pueda evaluar la calidad de tu interacción con la IA. Como en el ejemplo anterior, pide a la IA que proponga distintas arquitecturas para el módulo, y que explique las ventajas e inconvenientes de cada una. Elige la que consideres más adecuada para tu diseño y justifica tu elección en el documento de texto.

Simulación

Todos los módulos deben ser simulados de forma independiente utilizando testbenches específicos. La verificación de cada bloque debe cubrir casos de prueba relevantes que validen la funcionalidad de cada módulo.

Podemos pedir a las herramientas de IA que nos proporcionen testbenches para cada módulo. Revisalos, usualmente solo cubren casos básicos, por lo que es necesario diseñar tests para los casos límite (corner cases)

Trabajo en VIVADO

Incluye los archivos VHDL creados en las carpetas rtl/ y sim/, para incluirlos

en tu proyecto Vivado, puedes volver a crear el proyecto utilizando el

script scripts/lab.tcl (el proyecto debe estar cerrado antes de ejecutar el script).

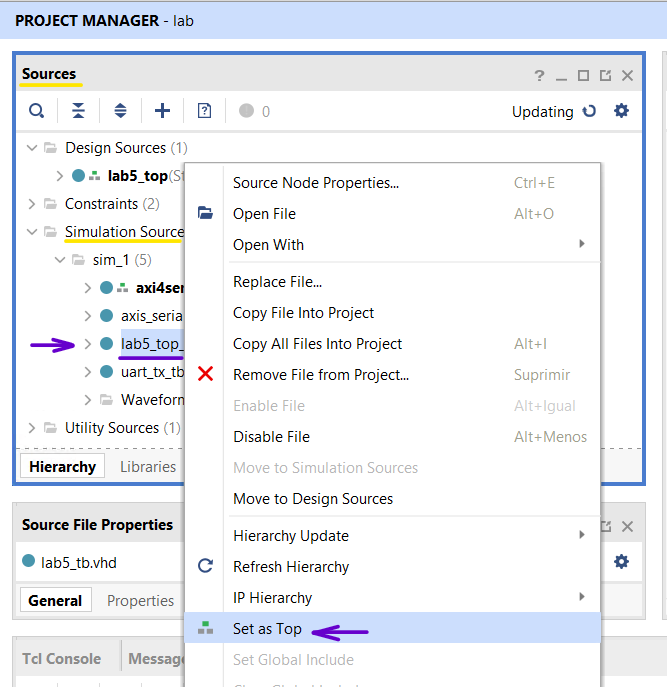

En Vivado puedes seleccionar el testbench a simular haciendo click derecho sobre el fichero en la pestaña Sources y seleccionando «Set as Top». Para ejecutar la simulación, haz click en «Run Simulation» y selecciona «Run Behavioral Simulation».

Advertencia

Es responsabilidad del estudiante revisar y validar el código generado por IA para asegurar su correcto funcionamiento.